# HAE504E Architecture – TP1

# **Objectifs:**

- Se familiariser avec le logiciel Archi\_la\_Simu accessible via le lien : <a href="https://dl.eea-fds.umontpellier.fr/ArchiLaSimu/">https://dl.eea-fds.umontpellier.fr/ArchiLaSimu/</a>

- Réaliser quelques instructions.

#### Présentation de l'outil :

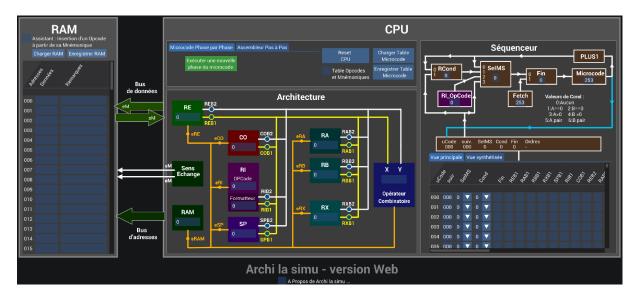

La vue générale de l'outil est représentée ci-dessous :

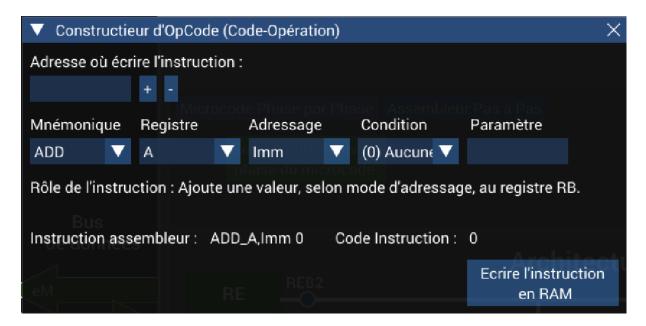

• RAM : Cette zone représente la mémoire RAM permettant de stocker le programme ainsi que les données manipulées par le programme. En cliquant sur « Assistant : insertion d'un Opcode à partir de sa mémonique » vous obtiendrez la fenêtre suivante qui va vous permettre de composer une instruction.

Vous avez à choisir l'adresse à laquelle sera écrite l'instruction ainsi que l'instruction elle-même. Pour ajouter une donnée ou une adresse en mémoire (dans le cas d'adressage Direct, Indirect etc ...), vous avez juste à cliquer dans la mémoire et à renter au clavier la valeur souhaitée.

- **CPU**: Cette zone représente le CPU (unité de traitement) avec la partie architecture (les différents registres et l'opérateur) ainsi que le séquenceur.

- Dans la partie architecture vous pouvez accéder manuellement aux contenus des registres. De plus, cette zone sera animée lors de l'exécution des instructions.

- La partie séquenceur va vous permettre de micro-coder des instructions. Deux vues sont possibles « Vue principale » développant l'ensemble des signaux de l'architecture et « Vue synthétisée » faisant apparaître uniquement les signaux utilisés. C'est cette dernière vue qui est préconisée pour réaliser les différents exercices.

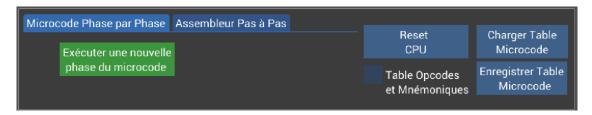

- Exécution du programme: En haut de la zone CPU vous trouverez les différentes options pour exécuter votre code (voir image ci-dessous). Le mode « Microcode Phase par Phase » est préconisé dans un premier temps. Il va vous permettre d'exécuter les instructions phase par phase afin de bien comprendre leur fonctionnement. Le mode « Assembleur Pas à Pas » exécute les instructions une à une. Ce mode est à utiliser si vos instructions sont correctes.

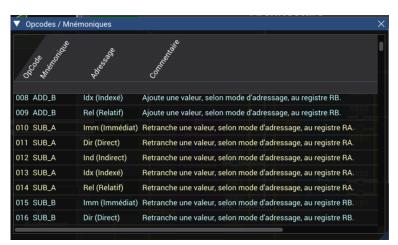

Dans la même zone, vous pouvez cliquer sur « Table Opcodes et Mnémoniques » pour connaître la position de chaque instruction (avec son mode d'adressage) dans la table du microcode du séquenceur. Vous pouvez aussi enregistrer ou charger votre table des microcodes.

**Attention :** Le logiciel est un logiciel en ligne, sans session. Il n'enregistre pas votre travail. Ainsi, si vous cliquez sur l'icône de rafraichissement de la page, tout le travail que vous avez réalisé est oublié!

## Mise en œuvre de l'outil :

Afin de prendre en main l'outil, vous devrez réaliser les exercices suivants :

## 1°) Cycle FETCH

Vérifier le contenu de la mémoire du séquenceur concernant le cycle Fetch. Reportez les phases dans le tableau ci-après.

#### 2°) Chargement de A en adressage immédiat

Donnez et reportez dans le tableau ci-après les phases de l'instruction :

LOAD A, Immédiat, 18

Implanter ces phases dans le séquenceur et exécuter l'instruction pour en vérifier le bon fonctionnement.

## 3°) Chargement de B en adressage direct

Donnez et reportez dans le tableau ci-après les phases de l'instruction :

LOAD B, Direct, 15

Implanter ces phases dans le séquenceur et exécuter l'instruction pour en vérifier le bon fonctionnement

# 4°) Branchement Inconditionnel - Adressage direct

Donnez et reportez dans le tableau ci-après les phases de l'instruction :

JUMP, Direct, 30

Implanter ces phases dans le séquenceur et exécuter l'instruction pour en vérifier le bon fonctionnement.

#### 5°) Branchement Conditionnel - Adressage relatif

Donnez et reportez dans le tableau ci-après les phases de l'instruction :

JUMP B pair, Relatif, 50

Implanter ces phases dans le séquenceur et exécuter l'instruction pour en vérifier le bon fonctionnement.

# Remplissez la mémoire des micro-programmes associés aux instructions utilisées :

LOAD A, Imm, 18 LOAD B, Direct, 15 JUMP direct, 30 JUMP B pair, Relatif, 50 STORE A, Indirect, 10

|          | AdrSuiv  | SelMS    | Cond      | FIN    | Ordres                                    |

|----------|----------|----------|-----------|--------|-------------------------------------------|

| 70       | 155      | 3        | -         | 0      | Ph4 : RIB1 XS eRA                         |

| 76       | 156      | 3        | -         | 0      | Ph4 : RIB1 XS eRAM                        |

| 81       | 161      | 3        | -         | 0      | Ph4 : RIB1 XS eRAM                        |

| 91       |          |          |           |        | Ph4: RIB1 XS eCO                          |

| 124      | -<br>158 | 3        | -         | 1      |                                           |

| 155      |          |          | -         | 0<br>1 |                                           |

| 156      | -        | -        | -         |        | Ph5 : COB1 PLUS1 eCO                      |

| 157      | -        | 0        | -         | 0<br>1 | Ph5 : sM COB1 PLUS1 eCO Ph6 : REB1 XS eRB |

|          | 100      | 1        | -<br>N° 6 |        |                                           |

| 158      | 160      | <u> </u> |           | 0      |                                           |

|          |          |          | pour B    |        |                                           |

| 150      |          |          | pair      | 4      | Db4 (condition foresce) : COR4 DLUC4 cCO  |

| 159      | -        | -        | -         | 1      | Ph4 (condition fausse): COB1 PLUS1 eCO    |

| 160      | -        | -        | -         | 1      | Ph4 (condition vraie) : COB1 RIB2 ADD eCO |

| 161      |          | 0        | -         | 0      | Ph5:sM                                    |

| 162      | -        | 0        | -         | 0      | Ph6: REB1 XS eRAM                         |

| 163      | -        | 0        | -         | 0      | Ph7: RAB1 XS eRE                          |

| 164      | -        | -        | -         | 1      | Ph8 : eM COB1 PLUS1 eCO                   |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

| 253      | -        | 0        | -         | 0      | COB1 XS eRAM                              |

| 254      | -        | 0        | -         | 0      | sM                                        |

| 255      | -        | 2        | -         | 0      | REB1 XS eRI                               |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

| $\vdash$ |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

| $\vdash$ |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |

|          |          |          |           |        |                                           |